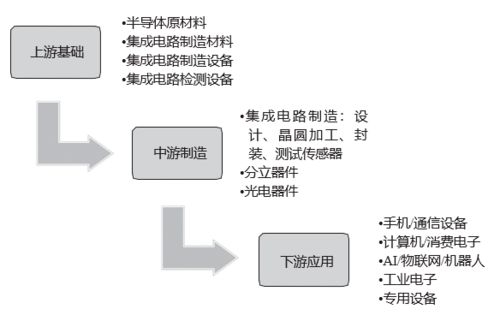

在集成電路(IC)設計與驗證流程中,Calibre是業界廣泛使用的物理驗證工具。設計工程師,尤其是在后端設計階段,常會遇到各種報錯,其中“Extra Pins”(多余引腳)報錯是一個典型問題。本文將簡要分析此報錯,并匯總包括EETOP、創芯網等在內的主流半導體技術論壇,為工程師提供問題排查與交流的平臺參考。

一、Calibre “Extra Pins” 報錯淺析

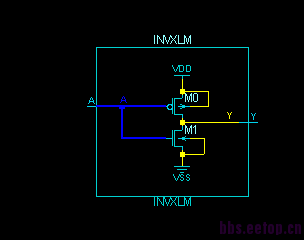

“Extra Pins”報錯通常發生在進行布局與布線(LVS)驗證時。其核心含義是:在提取出的版圖(Layout)網表中,存在某些電氣節點(即“引腳”),這些節點在對應的參考原理圖(Schematic)網表中并不存在。

可能的原因及排查思路:

1. 版圖繪制錯誤:最常見的原因。例如,在繪制版圖時,不小心多放置了未連接的金屬線、接觸孔或通孔,Calibre在提取時將其識別為一個獨立的電氣節點,從而被視為“多余引腳”。

2. 器件層次或屬性錯誤:某些器件的版圖形狀(如Guard Ring、Dummy Device)如果處理不當,可能被提取出額外的端口。

3. 電源/地網絡處理:如果版圖中的電源(VDD)、地(VSS)網絡名稱或連接方式與原理圖不完全一致,也可能引發此類報錯。

4. 文本層(Text Layer)誤標:錯誤的標簽(Label)放置,可能誤導提取工具識別出非預期的引腳。

解決步驟:

1. 仔細查看Calibre報錯報告,定位到具體的版圖坐標和網絡名稱。

2. 在版圖編輯工具(如Virtuoso)中跳轉到對應坐標,檢查該區域的圖形和連接。

3. 確認該節點是否確實為冗余圖形,若是則刪除;若非冗余,則需檢查其是否應與原理圖中的某個現有節點相連,或者原理圖是否需要相應修改。

二、后端設計與半導體技術交流論壇推薦

遇到復雜問題,自學排查往往效率有限。積極參與專業的技術社區討論,是工程師快速成長和解決問題的有效途徑。以下是一些在微電子、集成電路設計領域極具影響力的中文論壇:

- EETOP 創芯網論壇

- 定位:國內最知名、最活躍的集成電路與電子工程綜合社區之一。

- 優勢:

- 板塊全面:涵蓋數字前端/后端設計、模擬/RF IC設計、FPGA、嵌入式系統、半導體制造、EDA工具使用等多個子板塊。

- 資源豐富:擁有海量的學習資料、工具資源、技術文檔和面經分享。

- 用戶活躍:大量業內工程師、研究人員和學生聚集,Calibre等EDA工具的使用問題經常在此討論,很容易找到相關帖子和解決方案。

- 創芯網論壇(原“中國半導體論壇”)

- 定位:專注于半導體行業的技術與資訊交流平臺。

- 優勢:在產業新聞、工藝技術、芯片設計方面有深度討論,是了解行業動態和進行專業技術交流的好去處。

- 后端討論區(通常指各大論壇的子版塊)

- 在上述綜合論壇中,“數字后端設計”、“版圖設計” 等板塊是專門討論物理實現、靜態時序分析(STA)、形式驗證、物理驗證(如Calibre、PVS)等后端核心議題的集中地。在這里提問“Extra Pins”等具體問題,更容易得到后端同行針對性的解答。

三、給工程師的建議

- 善用搜索:在提問前,先在論壇內使用“Calibre Extra Pins”、“LVS 多余引腳”等關鍵詞搜索,很多常見問題已有詳細解答。

- 規范描述:發帖提問時,應清晰描述問題、所用工藝節點、EDA工具版本,并附上關鍵的報錯日志和截圖(注意脫敏),這能極大提高獲得有效幫助的概率。

- 跨界學習:集成電路設計是一個系統工程。后端工程師了解一些電路原理(前端),嵌入式工程師了解一些硬件特性(IC),都能拓寬解決問題的思路。這些論壇正是進行跨界知識補充的優質平臺。

面對Calibre等EDA工具報錯,系統性的自查與借助專業社區的力量相結合,是高效解決問題的關鍵。活躍于EETOP等工程師社區,不僅能解決眼前難題,更能持續跟蹤技術動態,與業界同行共同進步。