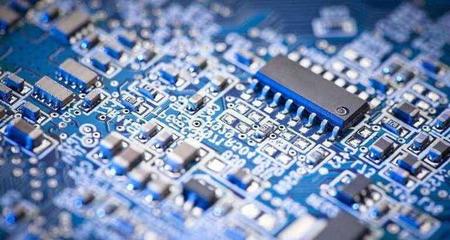

集成電路版圖設計是芯片制造過程中至關重要的一環,它直接決定了芯片的性能、功耗和可靠性。本文將從設計流程、常見挑戰和最佳實踐三個方面對集成電路版圖設計進行總結。

一、集成電路版圖設計的關鍵流程

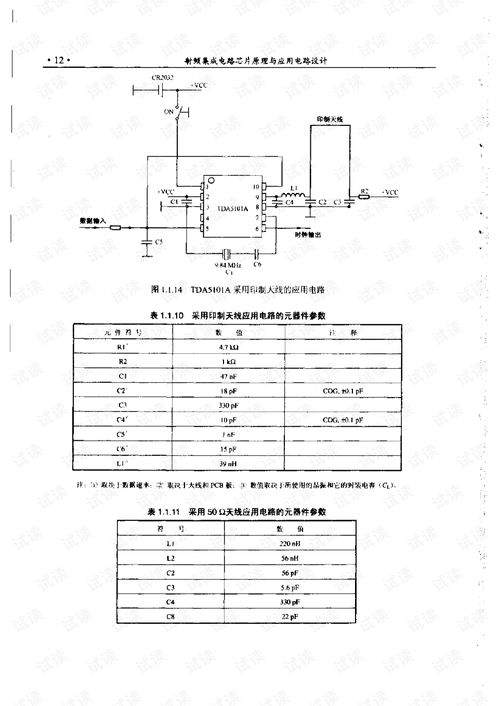

- 設計輸入:根據電路原理圖和設計規范,使用EDA工具(如Cadence Virtuoso)開始版圖設計。此階段需明確功能模塊劃分和總體布局。

- 布局規劃:確定芯片中各個功能模塊的位置,考慮信號流、電源分布和散熱需求。合理的布局能減少互連延遲和串擾。

- 單元放置:將標準單元或定制單元放置在預定位置,優化路徑以最小化時序問題和功耗。

- 布線:連接各個單元和模塊,確保信號完整性和電源穩定性。多層金屬布線技術常用于提高密度和性能。

- 驗證與仿真:通過DRC、LVS和ERC等檢查工具驗證版圖是否符合制造規則和電路功能。仿真工具用于預測時序、功耗和熱效應。

- 輸出與交付:生成GDSII文件等格式,交付給晶圓廠進行制造。

二、常見挑戰與應對策略

- 工藝變異:隨著工藝節點縮小,版圖設計需考慮制造過程中的變異,采用統計方法和冗余設計來提升良率。

- 功耗與散熱:高集成度導致功耗密度增加,版圖設計需優化電源網絡和散熱結構,例如使用多電源域和熱擴散層。

- 信號完整性:高速信號易受串擾和噪聲影響,通過屏蔽、差分布線和時序優化來緩解問題。

- 設計復雜性:現代芯片包含數十億晶體管,版圖設計需依賴自動化工具和團隊協作,采用分層設計方法以管理復雜度。

三、最佳實踐建議

- 早期規劃:在版圖設計前,與電路設計團隊緊密溝通,確保版圖符合性能目標。

- 使用先進EDA工具:利用工具自動化功能提高效率,例如自動布局布線(APR)和機器學習輔助優化。

- 持續驗證:在設計的每個階段進行多次驗證,避免后期返工,縮短開發周期。

- 學習最新工藝:緊跟半導體工藝發展,適應新規則和材料,例如FinFET和3D集成技術。

- 團隊培訓與知識共享:定期培訓設計人員,分享經驗教訓,提升整體設計水平。

集成電路版圖設計是一個多學科交叉的領域,要求設計者具備扎實的電子學知識、熟練的工具使用能力和對制造工藝的深刻理解。通過系統化的流程、積極的挑戰應對和持續的最佳實踐,可以有效提升芯片的成功率和競爭力。